金士顿量产镜像文件

(如何下载金士顿量产镜像文件)

作者 | 金捷幡

来源 | 金捷幡(ID:jin-jiefan)

《内存故事》主要是三年前写的。利用这个假期写一个短篇小说,无聊地鸟瞰近年来内存行业的一些现状。

现阶段内存领域存在哪些问题?

内存是一个不太好的俗称,主要用途有两个:作为程序运行的空间(DRAM等)和存储数据的空间(NAND等)。

NAND进入3D时代过后,容量基本上没有天花板,所以我们最后再谈。

现阶段的主要问题是DRAM:单位价格容量增长缓慢,速度跟不上CPU。这一问题在数据中心、高性能计算和运营商网络等商业领域尤为明显。

此外DRAM能耗过高,因为它必须在每个时钟周期给小电容器充电。

电费是商业用户的主要成本。在移动设备上,DRAM也是电池的死敌。

历史上DRAM增加带宽只能增加延迟,那么如何增加缓存呢?问题是,SRAM和CPU你和我一样贵,六个晶体管可以存一个比特。Intel最强处理器Cache,也只有DRAM千分之一。

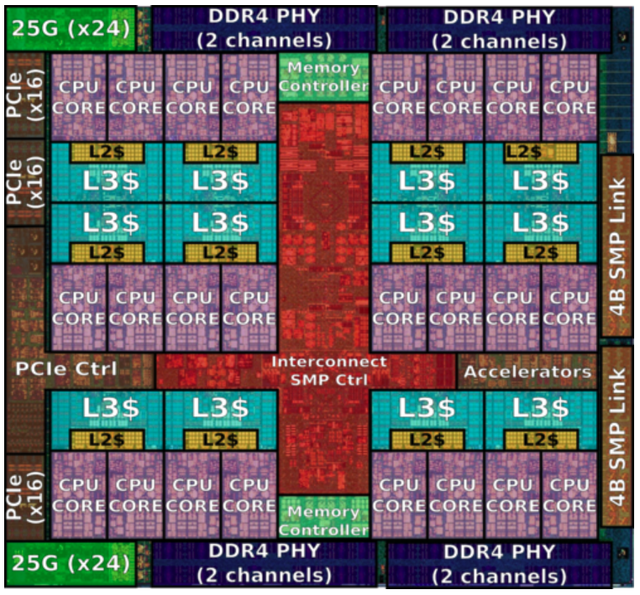

宇宙无敌的IBM Power 9 CPU配24个核也就120MB L代价是它的die size近700mm2,是苹果A处理器的七倍!

Power9中L2/L这么大的面积才100多M

内存行业的主要核心问题是容量、速度和功耗需求的增加DRAM技术瓶颈无法匹配。

DDR5

由于DRAM其自身的局限性,其技术进步一直十分痛苦。DDR3到DDR小进步花了五年时间;DDR从2012年第一版发布到今天DDR5未发布(注:显存)GDDR5只是DDR3的变种)。

DRAM标准由JEDEC JC-42制定工作组。虽然有投票机制,但DRAM其实节奏一直以英特尔为主。

原因很简单,英特尔肯定PC路线图:CPU或者北桥芯片决定何时支持新标准内存。

由于半导体工艺的进步,DDR5核心电压从DDR4的1.2V下降到1.1V,有望节省20%的功耗。

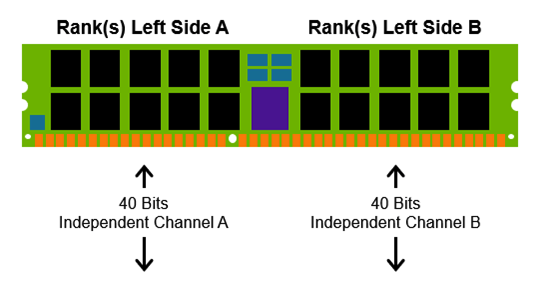

DDR5可使系统通道数翻倍,图:Mircon

DDR5的Burst Length和Prefetch (预读取)从DDR4的8n增加到16n,当时钟频率不变时,带宽翻倍。控制高速带来的各种信号干扰和抖动问题,DDR5还引入了核心时钟的各种优化调整。新的On-die ECC功能对服务器也有好处。

但这也将带来更多的设计、测试和兼容性挑战,需要CPU(包括内存控制器)巨大变化,从现在到2022年到2022年。

LPDDR5

低功耗LPDDR单独拿出来是因为从LPDDR从标准开始DDR分道扬镳。

虽然LPDDR5和DDR许多使用的新技术都很常见,但重点却大不相同。LPDDR5.功耗第一速度第二,DDR追求速度第一功耗第二。

因为LPDDR4已经是16n预读取,LPDDR5主要靠Bank group提高访问速度。它追求超低功耗,因此电源电压与核心电压比DDR5都更低。

x英特尔减缓了86领域的技术进步,但在手机领域却有所不同。

激烈的竞争和每年一次的旗舰产品发布,让每个家庭都在争夺最新的技术。

LPDDR就是一个例子。

小米10率先使用LPDDR5确实是个big thing,这显示了高通激进的产品策略。一加8和三星S今年的跟进基本上决定了今年的高端基调。

华为则面临比较尴尬的处境,因为美商Micron是目前LPDDR主要供应商5。三星估计优先供应自己,Hynix似乎在标准DDR5更用心。在LPDDR在供应困难的情况下,华为是否应该在下一代麒麟提供支持,这是产品规划的两难境地。

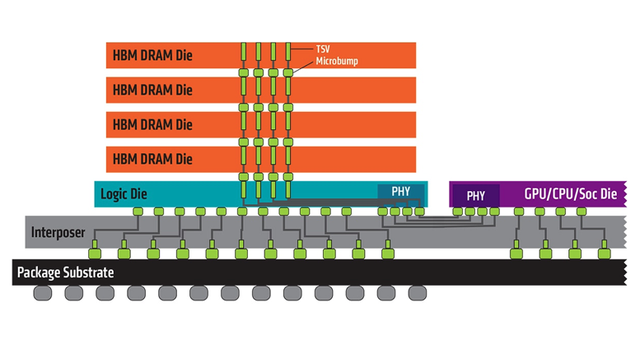

HBM

对于迫切需要高带宽的应用,如游戏和高性能计算,高带宽内存(HBM)则是绕过DRAM传统IO优秀的增强模式演进计划。

图:AMD

HBM与处理器直接包装的方式不再局限于芯片引脚,突破IO带宽瓶颈。另外DRAM和CPU/GPU物理位置的接近进一步提高了速度。

在尺寸上,HBM也可以大大降低整个系统的设计。

在目前,HBM很大程度上是GDDR6.竞争对手。但根据最新消息,Xbox Series X和索尼PS5仍旧选择了GDDR6,也许因为HBM成本高。

但从长远来看,DRAM仍有很强的3D化需求。因为2D制造(昂贵的10nm瓶颈)靠近天花板。

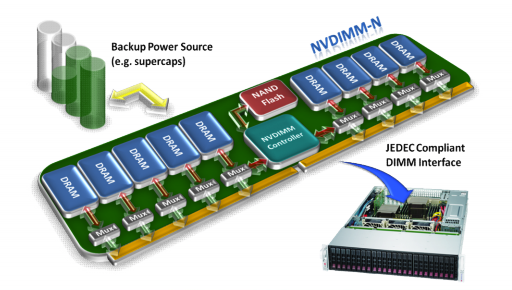

NVDIMM

现在云计算虚拟机和各种内存数据库都很流行,服务器对大容量内存非常渴望。但是由于DRAM成本难以进一步降低,如何低成本配置高容量内存成为难题。

混搭的NVDIMM被提起。

NVDIMM-F是直接用NAND颗粒替代DRAM制作内存条的好处是极其便宜,但速度太慢,无法突破系统DRAM访问限制总容量。

NVDIMM-N添加内存条NAND做DRAM镜像存储,防止服务器意外断电丢失内存数据。但NAND不能扩大内存,占用一些通道带宽。

JEDEC NVDIMM-N示意图

最终计划是NVDIMM-P,它允许巨大的容量,如1T内存允许使用各种新芯片,如NAND、RRAM、MRAM等替代DRAM。

还没看到JEDEC NVDIMM-P标准出来了。但是英特尔已经发布了3D-Xpoint为基础的Optane DIMM,支持自己的平台是一个巨大的优势,也是竞争对手的一个大门槛。

3D-Xpoint和其它NV内存

3D-Xpoint这是一个非常有趣的话题,声称速度比NAND快1000倍。

英特尔和Micron对3D-Xpoint技术原理一直保密,甚至根本没有透露。一开始有人猜是3D NOR,后来大家都以为是相变内存(PCM)或RRAM。

市场上没有人剥离芯片进行分析。

直到案卷,我们才能看到当代爱迪生Stanford Ovshinsky它的发明人。英特尔和和和Micron在Ovshinsky关键信息在公司破产处理中隐瞒。

和Micron分居后,英特尔3D-Xpoint不知道以后会不会有更多的小道消息转到大连厂独家生产。

3D-Xpoint技术在服务器领域有很大的增长潜力,但如何降低制造成本是关键。

MRAM、FRAM等其它NV类内存在物联网、汽车和工业等领域寻找机会。

MRAM工艺和传统MOS半导体工艺相似,有助于扩大生产,降低成本,最终有机会在一些嵌入式应用程序中取代部分NOR、SRAM或DRAM。

所以速度更快PCM和RRAM是否能取代NAND呢?由于存储数据的速度要求一般没有那么高,而且3D NAND低成本容量暴增太成功了。

图:比较不同内存的成本和速度

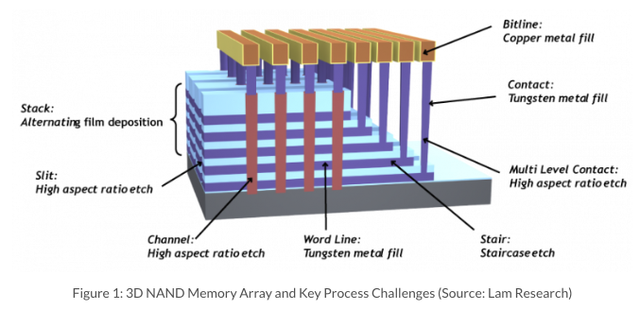

3D NAND

对于3D NAND来讲,单个cell缩小变得没有意义,因此不再需要最尖端的半导体制程技术。Hynix最近说,3D NAND未来可叠800层。

光刻环节减少,沉积和蚀刻过程大大增加,蚀刻之王泛林成为最大赢家。

另一个影响是DRAM和NAND生产线和产能不再灵活互补。

蚀刻下图这种楼梯达到百层,蚀刻长孔具有挑战性。楼梯是连接线,长孔是著名的充电陷阱(Charge Trap)。

记得英飞凌/奇梦达是以色列最早的Saifun公司技术量产Charge Trap闪存的。但当时技术不成熟,擦写寿命只有Floating Gate的1/10。Jim Handy说Charge Trap蚀刻孔的工艺来源于Trench技术。

在内存 60 年变史上提到的IBM、英飞凌,东芝和AMD早期半导体技术结盟,后来奇梦达用Trench独战群雄最终败北。但Charge Trap蚀刻技术继续存在:AMD的后代Spansion把它用在了NOR Flash上,东芝是领先的BiCS 3D NAND。

现在坚守Floating Gate只有英特尔一家。我的理解是FG每一层都需要光刻,这样的工艺复杂性会导致其失去竞争力,退出市场可能是不可避免的。

前几天看了128层长江的128层Xtacking该技术非常有趣,它将存储阵列与控制电路分开。这样可以大大降低开发和创新周期,但对量产的挑战并不小。具体技术细节不多,如果是的话wafer-to-wafer bonding,即使不考虑bonding成品良率是两片晶圆良率相乘的关系。

3D NAND的延续和DDR5标准难产是追赶中国内存业的好机会。

很高兴看到长信存储已经开始量产主流DDR4.知识产权和专利的远见布局也令人惊叹。

脚踏实地和雄心勃勃可能是内存行业的唯一途径。

参考阅读:

《内存故事》

《内存故事》-Rambus

《内存故事》-金士顿

声明:本文是作者的独立观点,不代表CSDN立场。

?Ruby 父亲:编程给程序员带来乐趣

?Zoom 如何击败科技巨头?

?视频 | 你不知道的\\"开源\\"60年秘史

?GitHub标星10,000 ,Apache项目ShardingSphere的开源之路

?阿里技术专家告诉你如何画出优秀的架构图?

?加拿大API平台如何实现30%的中国明星项目?创业老兵这么说……