2019年全国职业院校技能大赛(高职组) GZ-2019020 集成电路开发及应用赛项中第一部分集成电路设计与仿真的设计过程如下所示。

首先来看下题目:

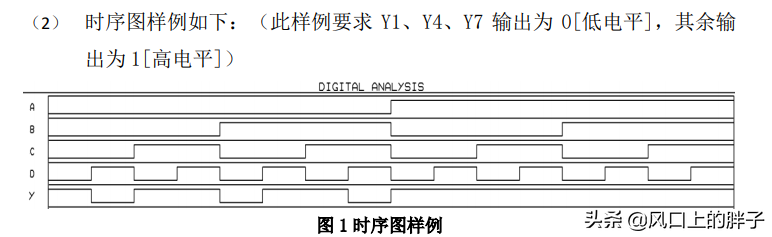

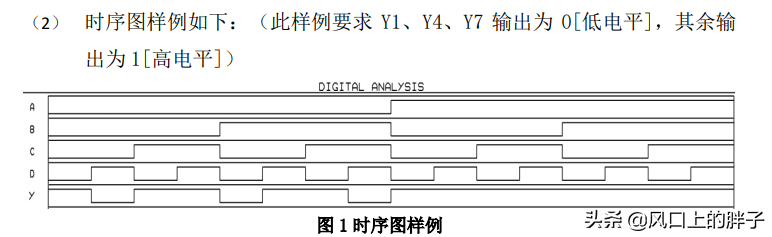

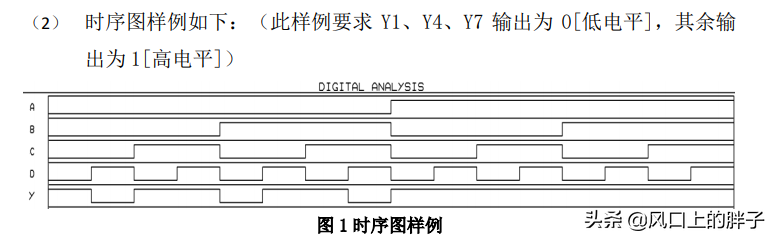

题目要求:设计的电路,输入端A、B、C、D按照下图所示时序输入信号,使得输出Y的波形需要按照下图所示。

题目分析

其实解决此题的思路与知识点也比较简单:利用到了《数字电路》里面由真值表转换逻辑函数表达式,利用CMOS管实现基本逻辑门电路,由逻辑函数表达式得出逻辑电路图,在 multisim软件上实现逻辑电路图等几部分知识。

那么由上可知,此赛题考查选手的《数字电路》基础知识以及multisim、proteus等仿真软件的使用熟练度。好的,知道上述解题思路之后,我们逐个来分析。

由真值表转换逻辑函数表达式

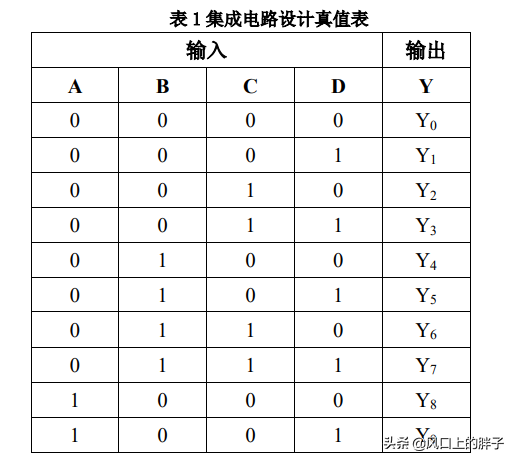

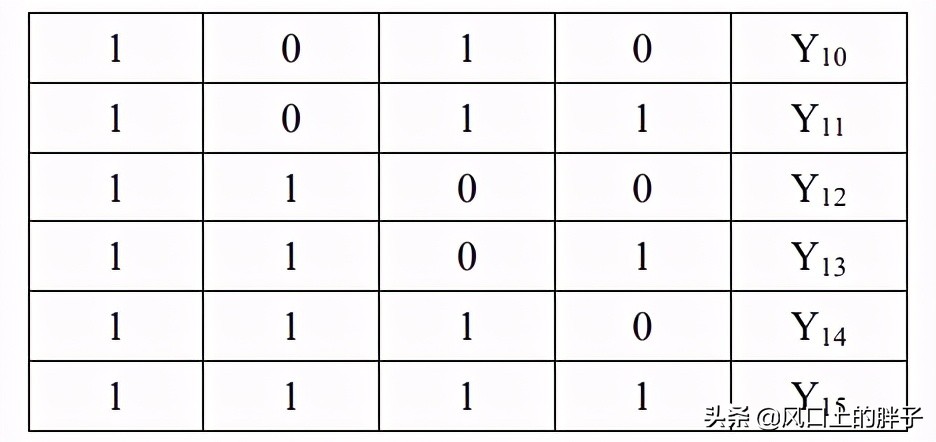

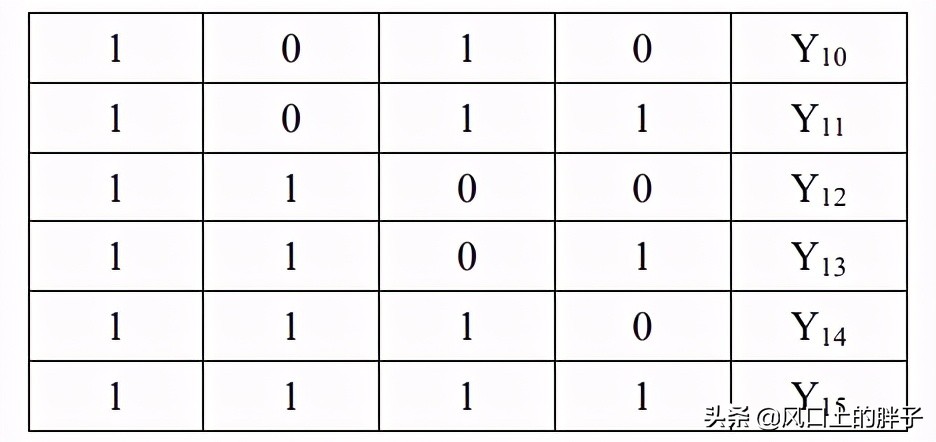

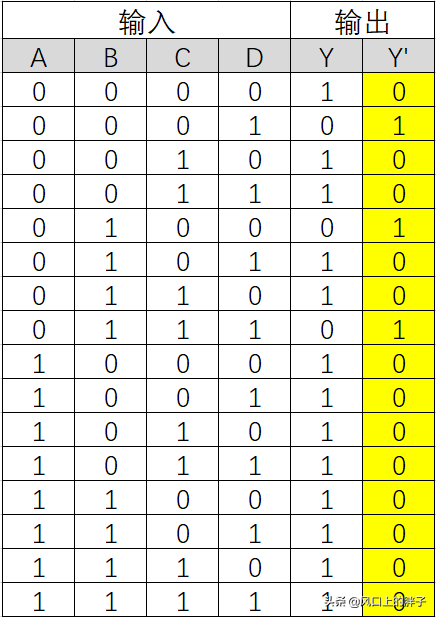

我们来看题目要求:此样例要求当输出Y处于Y1、Y4、Y7时刻的时候,Y输出0,其余时刻为1,为了更好地使读者明白,在下图进行了Y波形的划分说明。

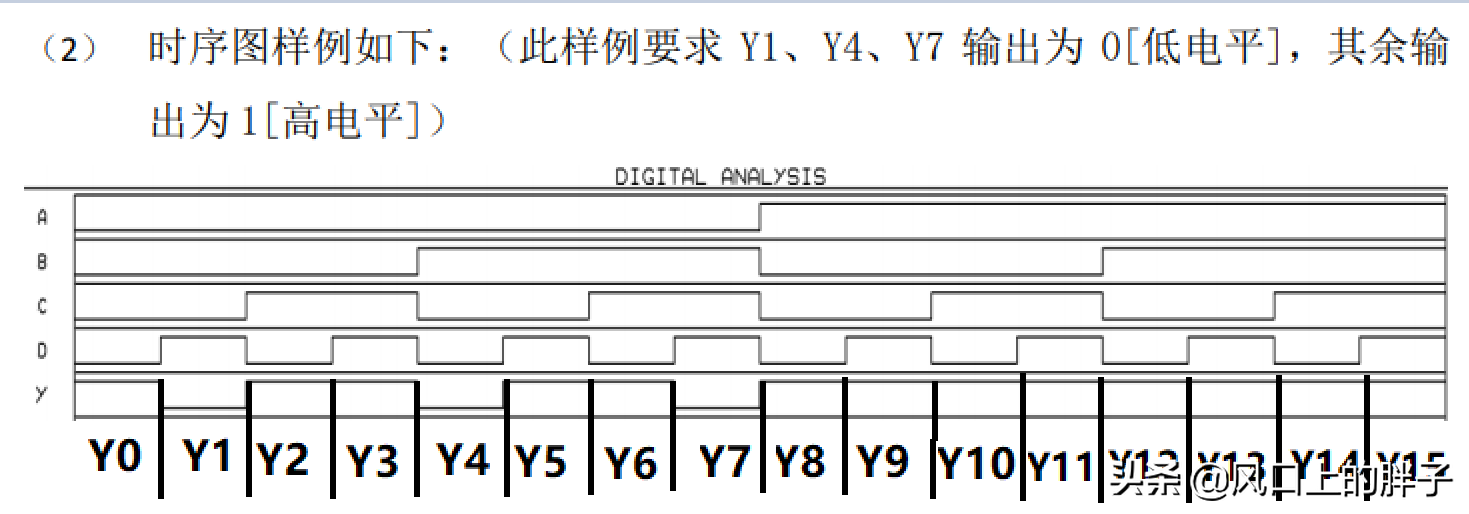

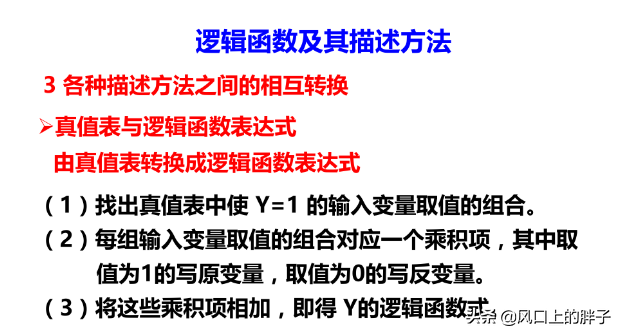

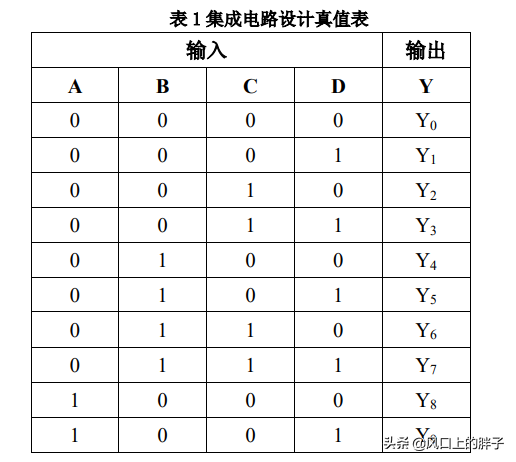

分析真值表,由真值表得出输出Y的逻辑函数表达式。我们可以一起来复习下,怎么由真值表得出逻辑函数表达式的过程。

真值表转换逻辑函数表达式

由上图真值表转换逻辑函数表达式可知,先找出使Y=1的输入变量组合,我们从题目要求可以知道,使Y=1的输入组合多达13项,这样我们得出Y的逻辑函数表达式将会很复杂,并且化简也困难,计算量也很大。我们注意到使Y=0的输入组合只有三项,输出Y处于Y1、Y4、Y7时刻的时候,Y输出0。

我们知道输出Y是一个二进制数据,如果对输出Y进行取反得到Y' (Y的反变量 ),那么Y'(Y的反变量)真值表就应该与Y相反,如下表所示。

经过这样的变换之后,求逻辑函数就变得简单了,

1、找出使Y'=1的输入项组合,然后这些输入项组合相或(在逻辑函数式上表现为相加);那么Y'=A'B'C'D A'BC'D' A'BCD 。进而求得Y= (Y')'=(A'B'C'D A'BC'D' A'BCD )'

PS:将真值表中的0看成反变量A',1看成原变量A,写出逻辑函数表达式就很简单了,如 输入组合0001(十进制1),对应A'B'C'D;又如输入组合0100(十进制4),对应A'BC'D'

同理输入组合0111(十进制7),对应A'BCD。

而题目中强调,当输出Y处于Y1、Y4、Y7时刻的时候,Y输出0(Y‘=1);

Y1、Y4、Y7的下标数字与上述输入组合的十进制一致。

举例:如果题目改成:当输出Y处于Y2、Y3、Y10时刻的时候,Y输出0(Y‘=1); 我们也能快速的写出逻辑函数表达式: Y2,Y3,Y10对应输入组合(0010 0011 1010), 那么Y'=A'B'CD' A'B'CD AB'CD'

利用CMOS管实现基本逻辑门电路

由于题目要求,必须用CMOS来设计电路,所以在由逻辑函数表达式转换逻辑图之前,我们还需要用CMOS管实现基本逻辑门电路。题目中已经提示在multisim中用ZVP2106G(PMOS管)和 ZVN2106G(NMOS管);

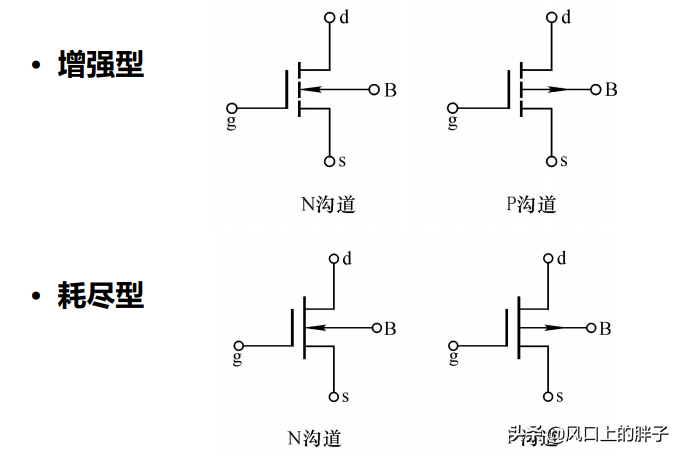

在看CMOS管构成门电路之前,复习下NMOS与PMOS的区别吧。

从上图,NMOS管与PMOS管的区别,在于PMOS管的中间箭头朝外(可以简单粗暴记忆:屁p朝外放),反之NMOS管中间箭头朝里。

(也可以认为NMOS管中间的沟道为N型 ,N是negative负极的首字母,P管中间沟道为P型的,P是Postive正极的首字母,而电流方向是正极流向负极的,所以PMOS中间沟道为正极P,所以电流流向外,那么箭头朝外。NMOS同理,箭头朝内)

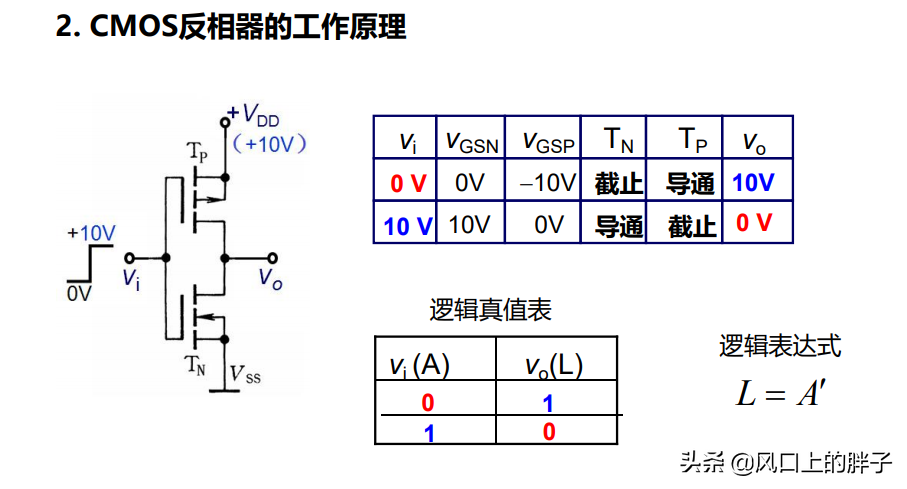

上图中,关于NMOS和PMOS管导通与截止,也可以简单的记忆,

NMOS管的栅极G(gate)给高电平导通,低电平截止。

PMOS管的栅极G(gate)给低电平导通,高电平截止。

接着我们来复习下,CMOS管实现基本逻辑门电路。

CMOS非门

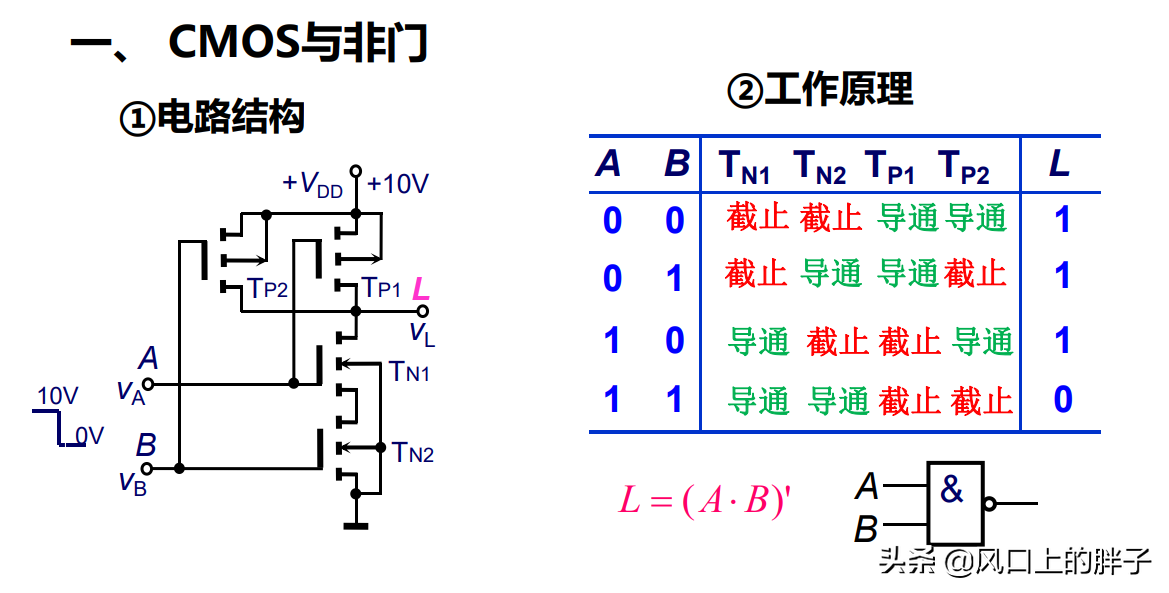

CMOS与非门

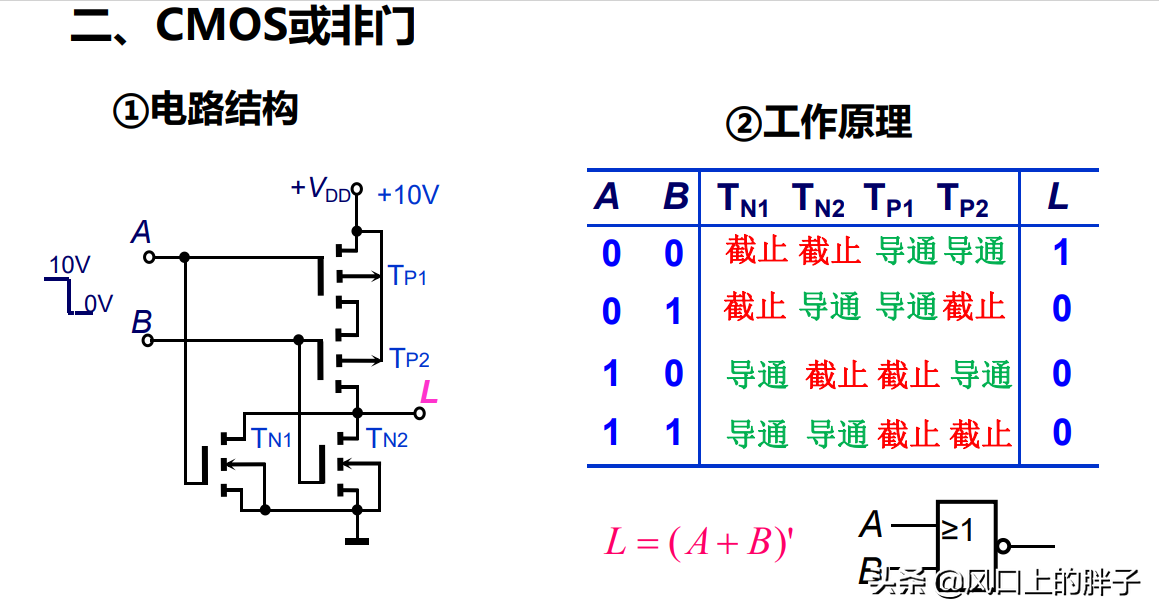

CMOS或非门

得到与非门、或非门要实现与门、或门也简单,在与非门后面再加入一个非门,即可得到与门,同理或门也是一样。

在multisim中验证CMOS门电路

我们做一个非常复杂的电路仿真,必须要将仿真分解成一个个小模块来逐个仿真实现,这样才能理清思路,也能避免一张图纸过于复杂,难以分析。这也是模块化设计的思想。

所以我们先用multisim软件来实现第四小节中所展示的CMOS门电路。

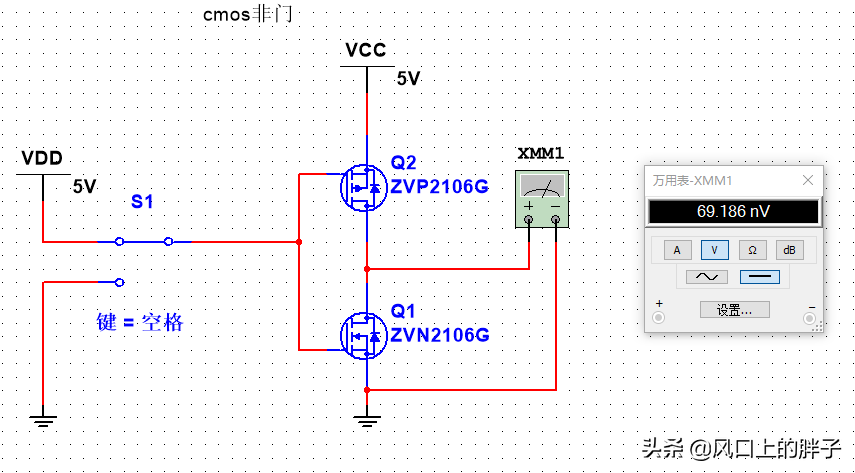

multisim实现CMOS非门

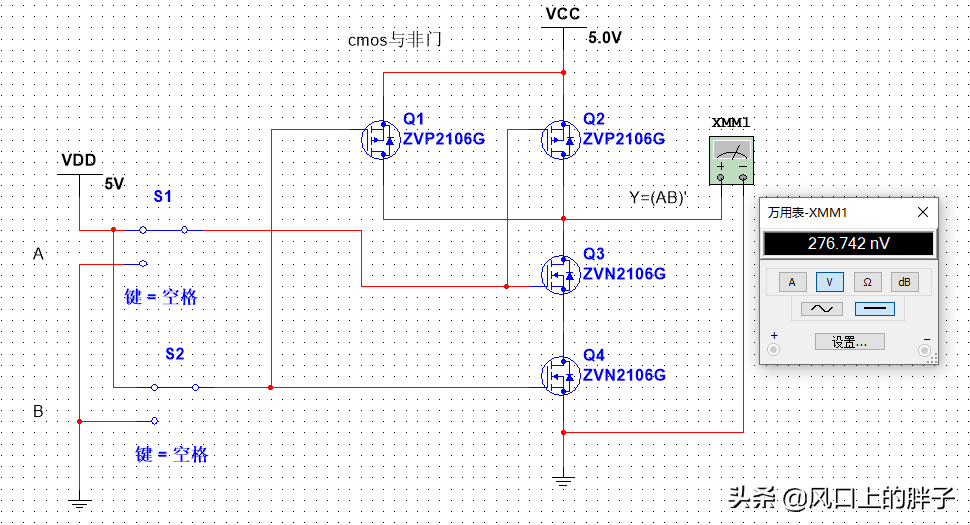

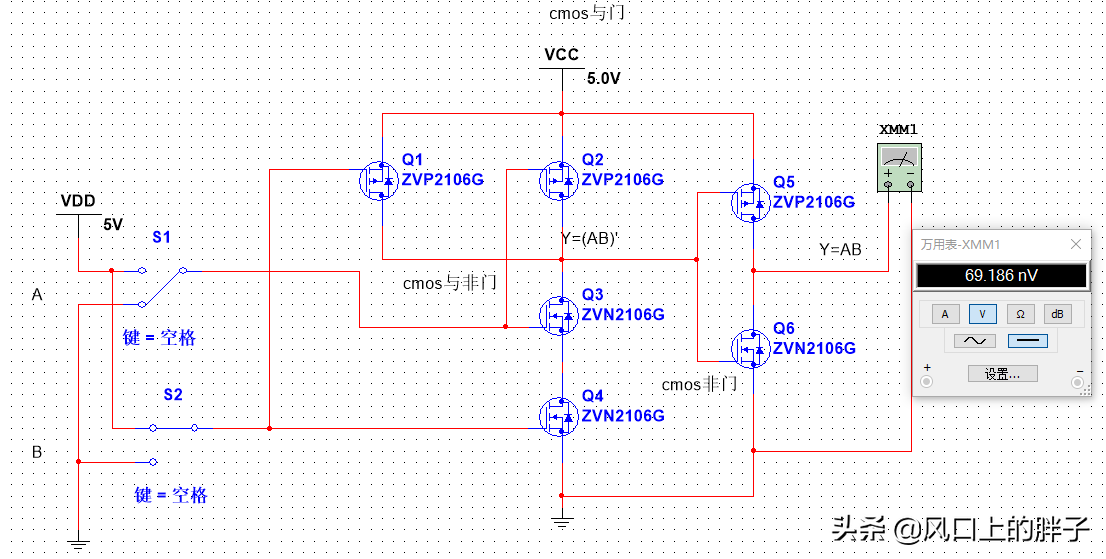

multisim实现CMOS与非门

multisim实现CMOS与门

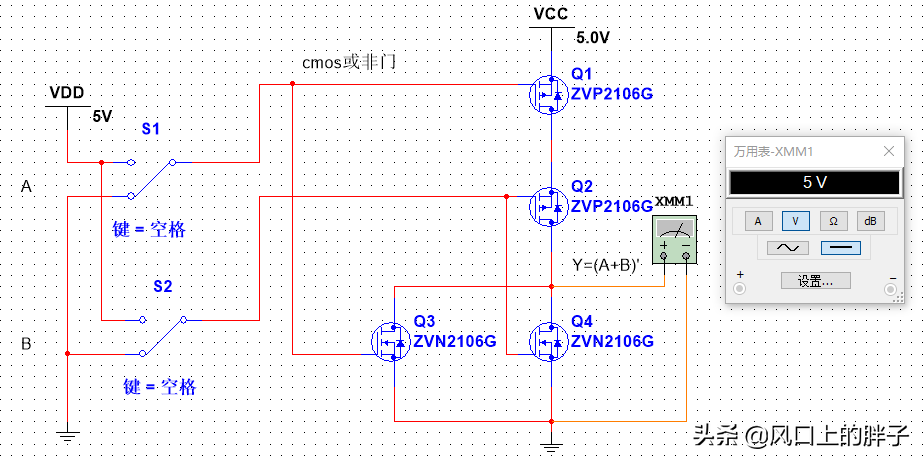

multisim实现CMOS或非门

在multisim中用层次原理图的方式实现逻辑函数表达式

根据第三小节中求得逻辑函数表达式Y=(A'B'C'D A'BC'D' A'BCD )' ,用CMOS管实现一个二输入的与门电路,图纸就已经非常大了,所以为了实现Y的逻辑函数,避免一张图纸放置太多的电路,这里在multisim软件中采用层次原理图的方式来实现,具体是用支电路(subcircuit)来设计电路。

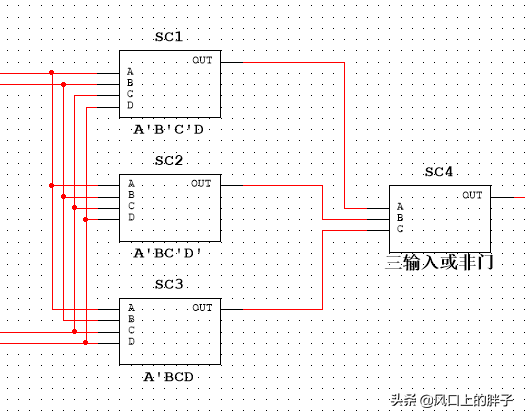

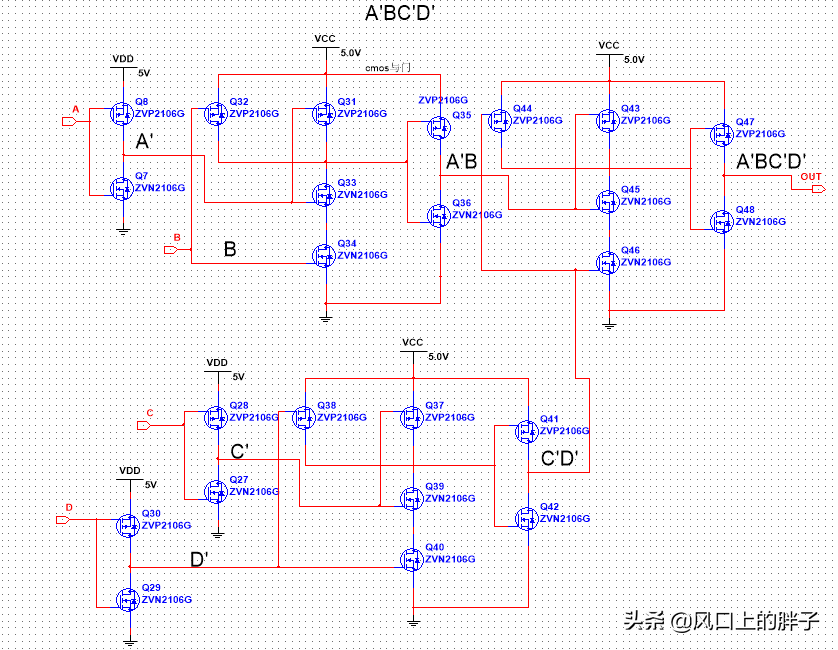

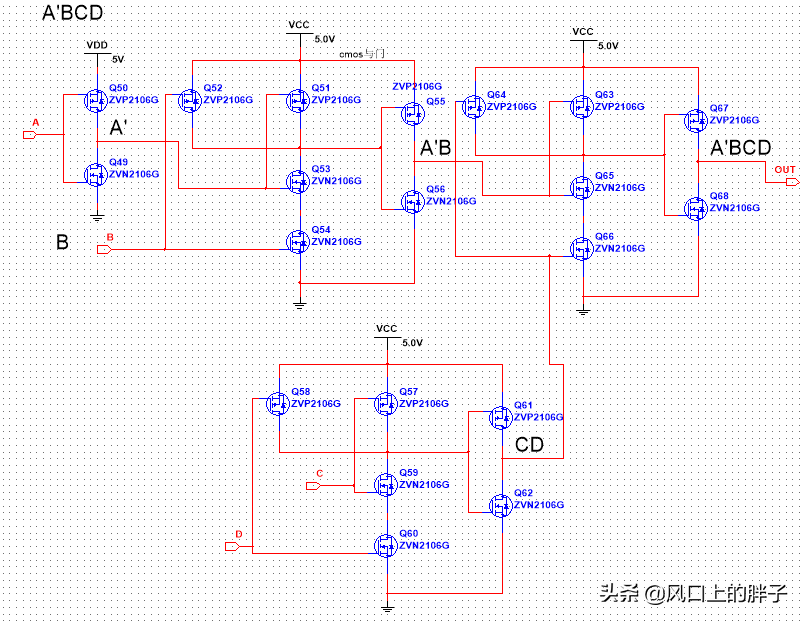

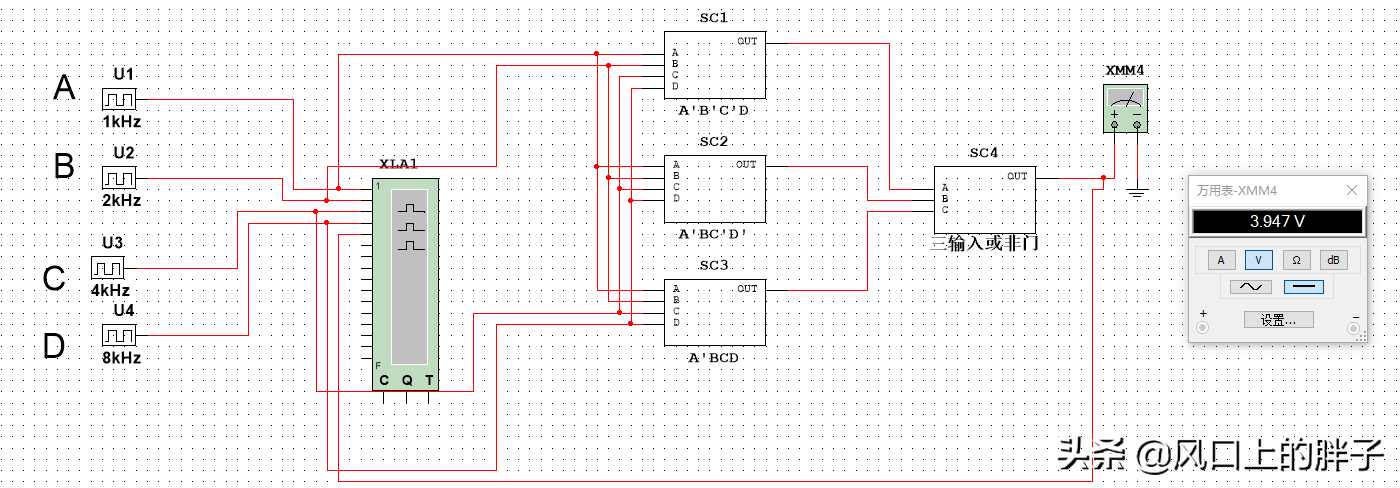

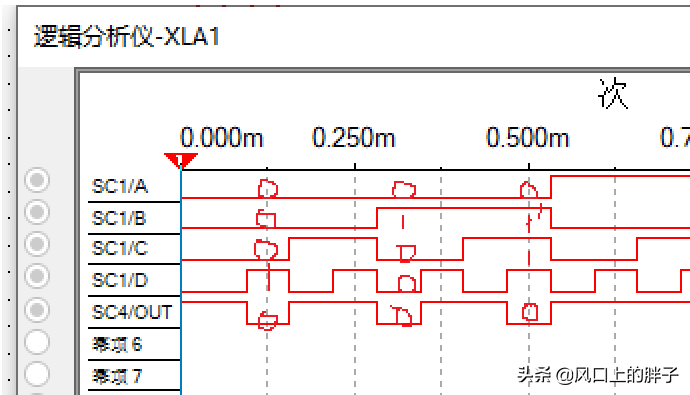

在一张主电路图纸中,分别新建四个支电路,如下图所示。支电路SC1实现A'B'C'D,SC2实现A'BC'D',SC3实现A'BCD,SC4是一个三输入或非门。

主电路

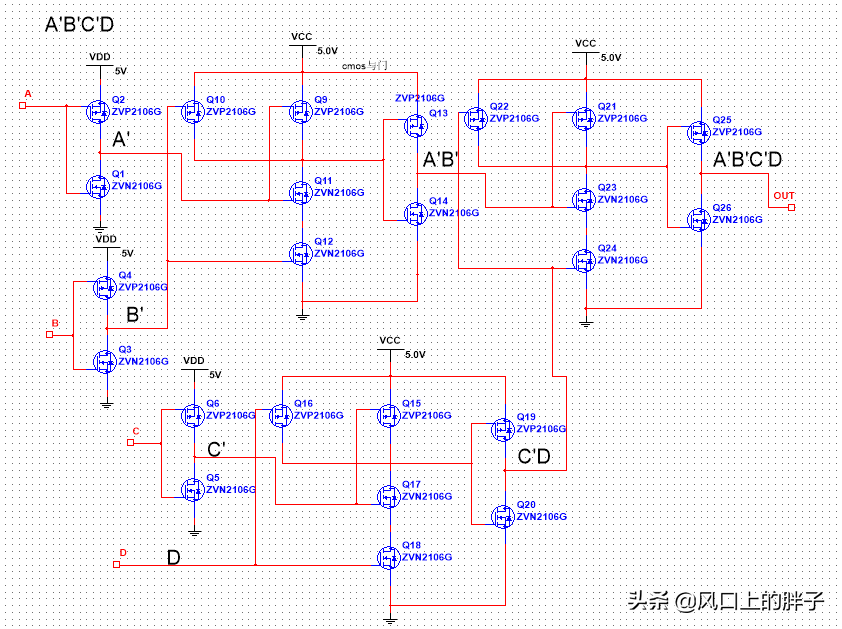

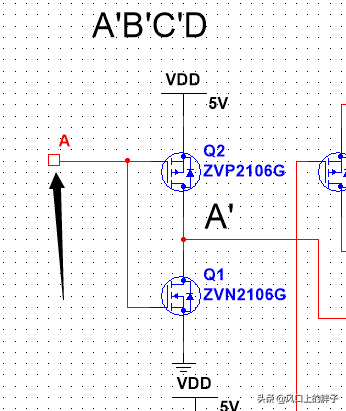

1、SC1内部电路图如下图所示:SC1实现A'B'C'D

SC1实现A'B'C'D

先用非门实现A',B',C',在用与门实现A'B'和C'D,最后用第二个与门实现A'B'C'D。

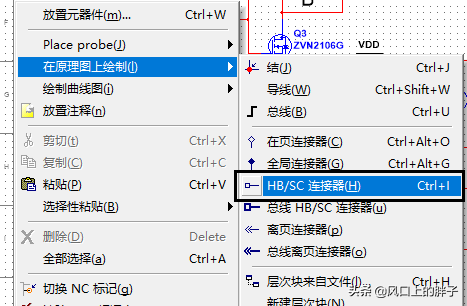

支电路中需要对外输出或者输入的端子添加HB/HC连接器

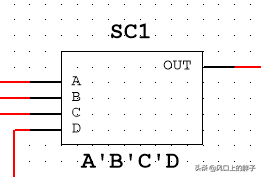

支电路中需要对外输出或者输入的端子,需要添加HB/HC连接器,这样在主电路中的SC1才能有引脚,如下图所示:

SC1中添加HB/SC连接器

主电路中SC1的引脚

2、SC2内部电路图如下图所示:SC2实现A'BC'D'

SC2实现A'BC'D'

3、SC3内部电路图如下图所示:SC3实现A'BCD

SC3实现A'BCD

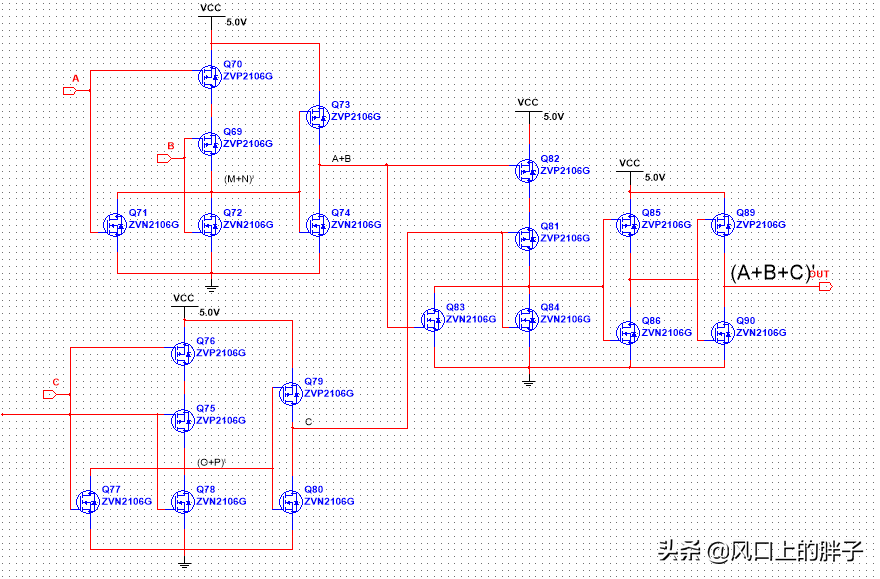

4、SC4内部电路如下图所示:SC4实现三输入或非门

SC4实现三输入或非门

5、主电路将几个支电路连接起来,如下图所示:

主电路

在主电路中,由于题目所给的时序图

时序图

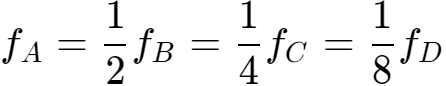

中隐含四个输入信号之间频率的关系是:

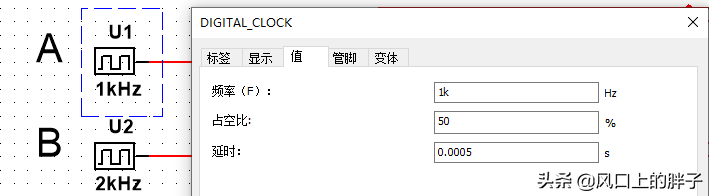

所以将主电路中的A,B,C,D信号的频率依次设置为1kHz,2kHz,4kHz,8kHz。

经过多次的实验测试,发现multisim中信号源无法设置相位,也就是无法设置方波从低电平开始输出。而我们题目中要求一开始产生的方波信号是从低电平开始,才能得出正确的波形图。解决办法是:所以为了实现正确的波形图,把各个信号源分别延迟1/2个周期,这样信号源的波形看起来就是从低电平开始输出了。

信号A延迟0.5ms输出

信号A延迟0.5ms输出,信号B延迟0.25ms输出,信号C延迟0.125ms输出,信号D延迟0.0625ms输出。

电路测试

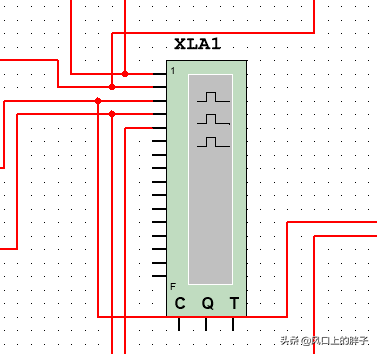

终于到了测试,这一环节!主电路中XLA1是逻辑分析仪,逻辑分析仪是利用时钟从测试设备上采集和显示数字信号的仪器,点击逻辑分析仪 - 快懂百科 了解更多关于逻辑分析仪。

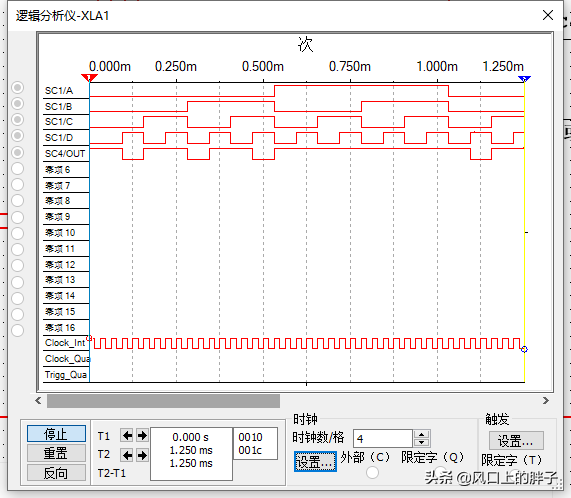

multisim中逻辑分析仪

multisim中逻辑分析仪使用,也非常简单,只需要将被测试的输入和输出信号连接到对应的通道即可。

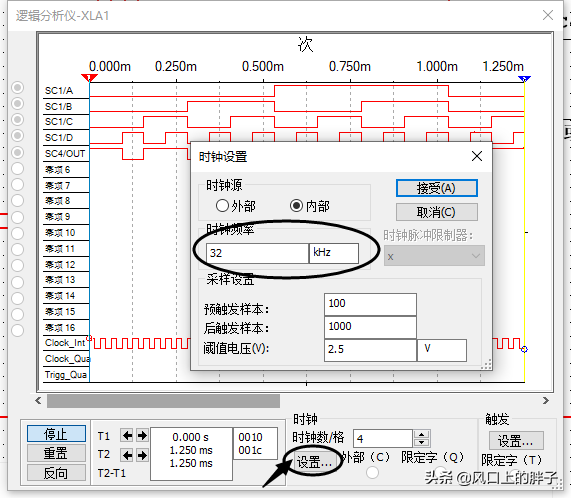

在multisim中开始仿真,双击逻辑分析仪XLA1,将逻辑分析仪的时钟源设置成内部,并且时钟频率为32kHz。采样定理 - 快懂百科

这里为什么要设置成32kHz,根据采样定理可知,当采样频率fs.max大于信号中最高频率fmax的2倍时(fs.max>2fmax),采样之后的数字信号完整地保留了原始信号中的信息,由于D通道的频率为16kHz,所以逻辑分析仪最小频率应该为2*16=32kHz。

逻辑分析仪采样频率设置为32kHz

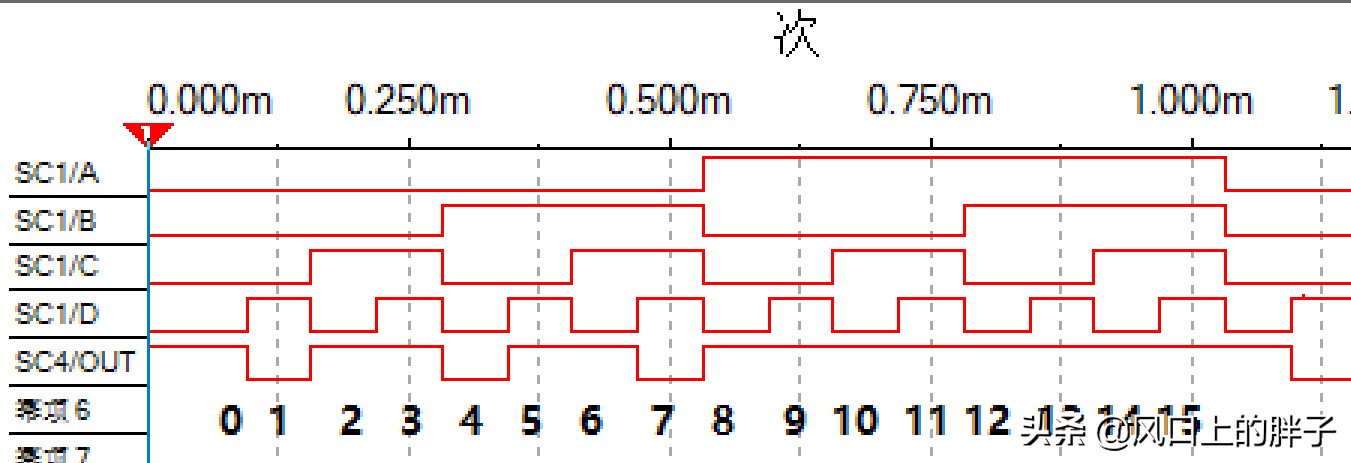

我们可以看到逻辑分析仪得到的时序波形与题目要求的时序波形一致。

逻辑分析仪显示的时序图

时序图

时序图分析

从逻辑分析仪获取到的时序图,我们可以得出很多信息,比如只有当输入组合为0001,0100,0111的时候,输出Y才会为0。

还比如信号输入ABCD,是按照二进制递增的方式来进行的。例如下图所显示的15,对应的ABCD输入为1111。

至此,这道集成电路设计题目的分析、设计、仿真的过程就全部介绍完毕了,谢谢!